#### "Ultra-Wideband for internet of things"

DIAL

Laurent, Gwendal

#### ABSTRACT

Over the past couple of years, big names in the technology industry like Apple and Samsung started to release ultra-wideband-based products. This radio technology can perform high data rate transmission with very low power consumption and has great resistance to multipath fading. Additionally, ranging applications built on top of ultra-wideband can perform distance measurements with an accuracy of a few centimeters. In this study, a driver is implemented for the GRiSP 2, a board for embedded systems and Internet of Things (IoT) running on the Erlang virtual machine out of the box. The driver is used to support a new sensor built by the company Peer Stritzinger GMbH based on the DWM1000 manufactured by the company Qorvo. This chip is IEEE 802.15.4-2011 compliant and uses ultra-wideband radio technology to send and receive data. On top of this driver, a simple medium access control (MAC) layer was built to send and receive MAC frames by following the IEEE 802.15.4-2011 standard. Finally, two-way ranging methods have been implemented to perform ranging operations between two GRiSP 2 cards. The results of this work show that the implementation is capable to send and receive MAC frames with a data rate of 31 kb/s and also perform accurate ranging operations.

**CITE THIS VERSION**

Laurent, Gwendal. *Ultra-Wideband for internet of things*. Ecole polytechnique de Louvain, Université catholique de Louvain, 2023. Prom. : Van Roy, Peter. <u>http://hdl.handle.net/2078.1/thesis:38375</u>

Le répertoire DIAL.mem est destiné à l'archivage et à la diffusion des mémoires rédigés par les étudiants de l'UCLouvain. Toute utilisation de ce document à des fins lucratives ou commerciales est strictement interdite. L'utilisateur s'engage à respecter les droits d'auteur liés à ce document, notamment le droit à l'intégrité de l'oeuvre et le droit à la paternité. La politique complète de droit d'auteur est disponible sur la page <u>Copyright</u> <u>policy</u> DIAL.mem is the institutional repository for the Master theses of the UCLouvain. Usage of this document for profit or commercial purposes is stricly prohibited. User agrees to respect copyright, in particular text integrity and credit to the author. Full content of copyright policy is available at <u>Copyright policy</u>

École polytechnique de Louvain

# Ultra-Wideband for internet of things

Author: **Gwendal LAURENT** Supervisor: **Pr. Peter VAN ROY** Readers: **Peer STRITZINGER, Pr. Ramin SADRE** Academic year 2022-2023 Master [120] in Computer Science

#### Abstract

Over the past couple of years, big names in the technology industry like Apple and Samsung started to release ultra-wideband-based products. This radio technology can perform high data rate transmission with very low power consumption and has great resistance to multipath fading. Additionally, ranging applications built on top of ultra-wideband can perform distance measurements with an accuracy of a few centimeters.

In this study, a driver is implemented for the  $GRiSP\ 2$ , a board for embedded systems and Internet of Things (IoT) running on the Erlang virtual machine out of the box. The driver is used to support a new sensor built by the company Peer Stritzinger GMbH based on the DWM1000 manufactured by the company Qorvo. This chip is IEEE 802.15.4-2011 compliant and uses ultra-wideband radio technology to send and receive data. On top of this driver, a simple medium access control (MAC) layer was built to send and receive MAC frames by following the IEEE 802.15.4-2011 standard. Finally, two-way ranging methods have been implemented to perform ranging operations between two  $GRiSP\ 2$  cards.

The results of this work show that the implementation is capable to send and receive MAC frames with a data rate of 31 kb/s and also perform accurate ranging operations.

#### Acknowledgements

I would like to express my gratitude to my thesis supervisor Professor Peter Van Roy for his guidance and assistance at every step of my thesis. Moreover, I would like to thank him for giving me the opportunity to work on this subject.

I also would like to thank Peer Stritzinger for all the invaluable advice and insights he provided me over the course of this work.

Lastly, I would like to thank my family for their unwavering support.

### Contents

| Li       | st of | Figures                                                                                                                                     | VI     |

|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------|--------|

| A        | crony | ns                                                                                                                                          | VII    |

| 1        | Intr  | duction                                                                                                                                     | 1      |

|          | 1.1   | Related work                                                                                                                                | <br>2  |

|          |       | $1.1.1  GRiSP \qquad \dots \qquad $ | <br>2  |

|          |       | 1.1.2 Ultra-Wideband (UWB)                                                                                                                  | <br>2  |

|          | 1.2   | Use cases                                                                                                                                   | <br>3  |

|          |       | 1.2.1 Real-time locating system (RTLS)                                                                                                      | <br>3  |

|          |       | 1.2.2 Communications                                                                                                                        | <br>3  |

|          |       | 1.2.3 Hera framework                                                                                                                        | <br>3  |

| <b>2</b> | Mat   | erial and resources                                                                                                                         | 4      |

|          | 2.1   | GRiSP                                                                                                                                       | <br>4  |

|          | 2.2   | Serial Peripheral Interface (SPI)                                                                                                           | <br>5  |

|          | 2.3   | Pmod & DWM1000                                                                                                                              | 5      |

|          |       | 2.3.1 Pmod drivers architecture of the $GRiSP$                                                                                              | <br>7  |

|          |       | 2.3.2 DW1000 register set                                                                                                                   | <br>8  |

|          | 2.4   | Ultra-Wideband $(UWB)$                                                                                                                      | 8      |

|          | 2.5   | IEEE 802.15.4-2011                                                                                                                          | 9      |

|          |       | 2.5.1 Ultra-Wideband PHY                                                                                                                    | <br>9  |

|          |       | 2.5.2 MAC sub-layer $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                        | 11     |

| 3        | Imp   | ementation of the driver                                                                                                                    | 14     |

|          | 3.1   | Interaction with the pmod                                                                                                                   | <br>14 |

|          |       | 3.1.1 Transaction format                                                                                                                    | 16     |

|          |       | 3.1.2 Example                                                                                                                               | <br>17 |

|          | 3.2   | Mapping the registers                                                                                                                       | 18     |

|          |       | 3.2.1 Errors in the user manual                                                                                                             | 19     |

|          |       | 3.2.2 Read the registers $\ldots$                          | 20     |

|          |     | 3.2.3 Write the registers $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 2$ |

|----------|-----|----------------------------------------------------------------------------------------------|

|          | 3.3 | Initialization of the pmod                                                                   |

|          |     | 3.3.1 Checking the connected device                                                          |

|          |     | 3.3.2 Loading the leading edge algorithm                                                     |

|          |     | 3.3.3 Writing optimal values                                                                 |

|          |     | 3.3.4 Writing custom configuration                                                           |

|          |     | 3.3.5 Setting up SFD                                                                         |

|          | 3.4 | Transmission 2                                                                               |

|          |     | 3.4.1 Sending a frame                                                                        |

|          |     | 3.4.2 Receiving a frame                                                                      |

| 4        | MA  | C layer 3                                                                                    |

|          | 4.1 | DW1000 support                                                                               |

|          |     | 4.1.1 Frame filtering                                                                        |

|          |     | 4.1.2 CRC generation and checking                                                            |

|          |     | 4.1.3 Automatic acknowledgement                                                              |

|          | 4.2 | MAC Header                                                                                   |

|          | 4.3 | Transmission                                                                                 |

|          |     | 4.3.1 Sending                                                                                |

|          |     | 4.3.2 Receiving                                                                              |

|          | 4.4 | Example: Using the automatic acknowledgment feature of the DW1000 3                          |

|          | 4.5 | Measurements                                                                                 |

|          |     |                                                                                              |

| <b>5</b> | Two | way ranging 3                                                                                |

|          | 5.1 | Methods                                                                                      |

|          |     | 5.1.1 Single-sided two-way ranging                                                           |

|          |     | 5.1.2 Double-sided two-way ranging                                                           |

|          | 5.2 | Implementations                                                                              |

|          |     | 5.2.1 Single-sided two-way ranging                                                           |

|          |     | 5.2.2 Double-sided two-way ranging                                                           |

|          |     | 5.2.3 Counter wrap around $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 4$        |

|          | 5.3 | Measurements                                                                                 |

| 6        | Con | clusion 4                                                                                    |

|          | 6.1 | Future work                                                                                  |

|          |     | 6.1.1 Improvement of the driver                                                              |

|          |     | 6.1.2 MAC layer                                                                              |

|          |     |                                                                                              |

|          |     | 6.1.3 Upper layers                                                                           |

|          |     |                                                                                              |

| 7 | Bibliography                                                                                                            | 52                      |

|---|-------------------------------------------------------------------------------------------------------------------------|-------------------------|

| A | Driver code                                                                                                             | 55                      |

| в | MAC layer code                                                                                                          | 103                     |

| С | Examples         C.1 ack_no_jitter         C.2 ack_jitter         C.3 ack_fast_tx         C.4 ss_twr         C.5 ds twr | . 115<br>. 118<br>. 121 |

| D | MAC layer unit tests                                                                                                    | 130                     |

### List of Figures

| 1  | $GRiSP \ 2 \ (credits: grisp.org) \ \ldots \ $ | 4              |

|----|------------------------------------------------------------------------------------------------------------------------|----------------|

| 2  | DWM1000 (source: mouser.be)                                                                                            | 6              |

| 3  | The pmod uwb (left) connected to the $GRiSP \ 2$ (right) board $\ldots$                                                | $\overline{7}$ |

| 4  | IEEE 802.15.4-2011 types of topologies (credits: IEEE[1])                                                              | 10             |

| 5  | UWB PHY frame structure (credits: DW1000 user manual [2])                                                              | 10             |

| 6  | PHY header (PHR) bit description (credits [1])                                                                         | 11             |

| 7  | MAC Superframe (credits [1])                                                                                           | 12             |

| 8  | MAC frame and its fields (credits [2])                                                                                 | 12             |

| 9  | The frame control of the MAC header and it (credits $[2]$ )                                                            | 12             |

| 10 | DW1000 - SPIPHA = 1 (source: DW1000 data sheet [3]) $\ldots$                                                           | 15             |

| 11 | Different SPI transactions (source: DW1000 user manual $[2]$ )                                                         | 16             |

| 12 | One byte header (source: DW1000 user manual $[2]$ )                                                                    | 16             |

| 13 | Two bytes header (source: DW1000 user manual $[2]$ )                                                                   | 17             |

| 14 | Three bytes header (source: DW1000 user manual $[2]$ )                                                                 | 17             |

| 15 | Description of a read operation performed on the DEV_ID register                                                       |                |

|    | (source: DW1000 user manual $[2]$                                                                                      | 17             |

| 16 | Read transaction on DEV_ID showed on the logic analyser                                                                | 18             |

| 17 | Read API call on register $DEV_ID$                                                                                     | 20             |

| 18 | Write API call on register <i>PANADR</i>                                                                               | 21             |

| 19 | Write API call on register $PMSC$                                                                                      | 21             |

| 20 | Write API call on register $PMSC$ on multiple sub-registers and                                                        |                |

|    | sub-fields                                                                                                             | 22             |

| 21 | Setup of the SFD inside the code                                                                                       | 26             |

| 22 | Example of the statistical report for an exchange of 2000 frames                                                       |                |

|    | containing 116 bytes of data                                                                                           | 37             |

| 23 | Message exchanges of single sided two way ranging                                                                      | 40             |

| 24 | Message exchanges of double sided two way ranging                                                                      | 42             |

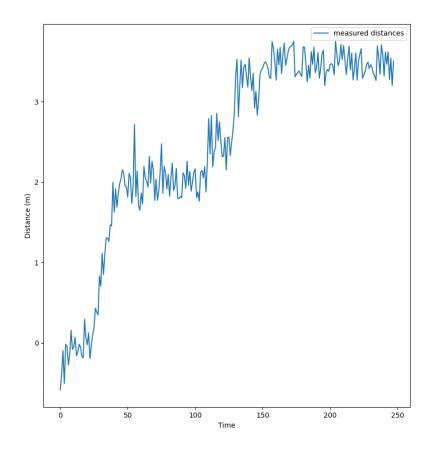

| 25 | Graph showing the measured distance                                                                                    | 47             |

#### Acronyms

AOA angle of arrival.

**BPM** Burst Position Modulation.

BPSK Binary Phase-Shift Keying.

**BSP** Board Support Packages.

CAP contention access period.

**CFP** contention-free period.

**CMOS** Complementary metal–oxide–semiconductor.

**CSMA-CA** Carrier-sense multiple access with collision avoidance.

FCS frame checking sequence.

${\bf FDT}\,$  Flattened Device Tree.

${\bf FEC}\,$  Forward error correction.

**GTS** guaranteed time slots.

**IoT** Internet of Things.

LR-WPAN low-rate wireless personnal area networks.

$\mathbf{MAC}\ \mathrm{medium}\ \mathrm{access}\ \mathrm{control}.$

$\mathbf{MFR}\ \mathrm{MAC}$  footer.

$\mathbf{MHR}\ \mathrm{MAC}$  header.

MISO Master In-Slave Out.

${\bf MOSI}\,$  Master Out-Slave In.

**NIF** Native Implemented Function.

NiF Native-implemented Functions.

**PAN** Personal Area Network.

**PER** packet error rate.

PHR PHY header.

**PHY** physical layer.

**RTLS** real-time location system.

**SECDED** Single-error-correction double-error-detect.

**SFD** Start of frame delimiter.

SHR Synchronization header.

**SPI** Serial Peripheral Interface.

**SPICLK** clock signal.

${\bf SPICSn}$  slave select signal.

SPIPHA clock/data phase.

**SPIPOL** clock polarity.

**TDOA** time difference of arrival.

**TOF** time of flight.

ToF Time-of-Flight.

${\bf UWB}$  ultra-wideband.

### Chapter 1 Introduction

In our interconnected world, IoT has become omnipresent in our daily lives and is expected to grow and expand more with the arrival of 5G. However, among all technologies used in that ecosystem, one is being overlooked, ultra-wideband (UWB). This technology has been proven to be resistant to multi-path fading [4] and is also able to perform high data rate transmission using very low power consumption [5]. Additionally, UWB is capable to realize ranging measurements 100 times more accurately than other technologies like Bluetooth or WiFi [6]. In 2021, Apple released their AirTag product which uses UWB and Bluetooth technology to track everyday objects like a set of keys or a wallet. More recently, in 2023, Samsung also released their first UWB chipset, the Exynos Connect U100 which they claim is able to perform ranging operation "down to single-digit centimeters" [7]. These two examples show the industry's recent interest in the technology.

The company Peer Stritzinger GmBH is planning to release a new UWB pmod based on the DWM1000 chip manufactured by the company Qorvo for their last version of the *GRiSP* board, the *GRiSP* 2. A prototype has already been built, but the board needs to be extended with a new driver to support it. Qorvo already published a driver written in C [8], but isn't compatible with the *GRiSP* 2 because its runtime library is written in the Erlang programming language instead of C. With this driver, the company would be able to show potential clients how the new pmod will work and later on, build a new batch of pmod. Furthermore, a new version of the boards, the *GRiSP* 0, is planned to be released. This board would support only one radio interface. The first version of the *GRiSP* 0 should start by supporting UWB and the driver would allow them to release a first set of prototypes.

This work will show how the driver was built layer by layer before showing a couple of applications implemented on top of it. More precisely, chapter 2 will give an overview of the different technologies and materials used in this study. Chapter 3 will explain the implementation of the driver which includes read and

write operations to the different registers of the DW1000 as well as transmission and reception operations. Then chapter 4, describes how the MAC layer has been implemented on top of the driver to achieve transmission and reception of MAC frames. Afterward, chapter 5 uses the MAC layer to perform ranging operations using two different two-way ranging methods. Finally, chapter 6 gives a summary of all the results as well as a list of possible improvements that could be done on the driver and the upper layers.

The goals of the thesis are to be able to exchange reliably a series of MAC frames between two devices even in the presence of network jitter and to perform multiple series of distance measurements using the two-way ranging methods in different situations and assess the precision of their implementations.

#### 1.1 Related work

#### $1.1.1 \quad GRiSP$

The GRiSP project and more precisely, the GRiSP base board has been the basis of previous works. In [9], the authors developed a fault-tolerant and distributed framework for asynchronous sensor fusion called Hera using the GRiSP-Base board and Erlang. They showed how to perform sensor fusion for position and orientation tracking and how efficient it can be. In [10], the author built a driver for the MRF24J40 microchip to enable IEEE 802.1.4 based communications between GRiSP-Base boards and also with the Zoleria RE-MOTE using Contiki.

#### 1.1.2 Ultra-Wideband (UWB)

UWB isn't a new technology and past works like [11] and [12] were already claiming its potential and its possible applications in wireless personal area networks and sensor networks twenty years ago. In [13], it was shown that UWB radar systems are able to perform human detection through walls due to the technology's high range resolution and good penetration of obstacles. This kind of application can be used in emergency situations to find survivors inside buildings after earthquakes. Other applications use UWB combined with two-way ranging to localize objects. For example, this paper [14] uses the DW1000 to perform two-way ranging to build a localization system for drones performing inventory management. Moreover, UWB positioning measurements can be fused with the measurements of other sensors to get a more accurate and robust view of the environment. In [15], UWB position measurements were fused with an inertial measurement unit via an extended Kalman filter to build and assess an indoor positioning system.

#### 1.2 Use cases

This work opens the door for a large number of applications for the pmod UWB. Indeed, the implementation of the driver is only the first stepping stone of using UWB on the GRiSP. The applications and use cases presented in this section could have a massive impact on our daily lives.

#### 1.2.1 Real-time locating system (RTLS)

Multiple real-time location system (RTLS) applications have already been built using UWB. However, none were built using GRiSP. With the introduction of the pmod UWB in the GRiSP ecosystem, robust and low power RTLS applications will be possible. For example, on the industry level, such applications could perform smart inventory management or even localize equipment in a large warehouse.

Additionally, in healthcare RTLS has been used to locate patients inside a hospital in the case of emergencies or their activities inside their rooms. But also in the cases of Alzheimer's disease and dementia patients can be localized and be prevented from leaving the building by automatically locking doors for example [16] and a GRiSP based RTLS could extend the set of tools already existing.

Finally, in our daily lives, smart homes could use RTLS applications with *GRiSP* to locate objects in a house. Such applications could also be used on devices to make them more aware of their environment. For example, we could imagine autonomous robots like robotic vacuum cleaners using UWB to track down their position in a house and improve their efficiency.

#### **1.2.2** Communications

Besides ranging applications, the new pmod is also able to transmit data using the IEEE 802.15.4-2011 standard. With this driver, it will be possible to implement layers like 6LoWPAN on the GRiSP and perform low power communications with other GRiSP boards but also other devices running 6LoWPAN with UWB.

#### 1.2.3 Hera framework

The Hera framework already provides a sensor fusion for the Erlang programming language. In [9], the authors use the pmod MAXSONAR to achieve position tracking. Two-way ranging methods could be used to perform the same type of experiments with Hera and compare their results with the ones acquired with the pmod MAXSONAR.

# Chapter 2 Material and resources

#### 2.1 GRiSP

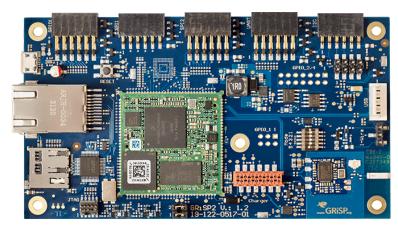

GRiSP [17] is a project developed by the company Peer Stritzinger GmbH. It combines both customizable hardware and software to provide embedded systems solutions.

The hardware, the board, has two versions. The first one is called the GRiSP-Base and the second one, the GRiSP~2, is its evolution. In the context of this master thesis, only the latest version will concern us. The GRiSP boards have multiple sockets to connect different modules called Pmods that can be connected through multiple interfaces like GPIO and SPI.

Figure 1: GRiSP 2 (credits: grisp.org)

The software runs on a custom open-source operating system that combines both Erlang and RTEMS (Real-time executive for multiprocessor systems) a realtime operating system that supports 18 processor architectures and open standard application programming interfaces [18]. This combination enables the board to run Erlang code out of the box and lets users create IOT applications directly in that programming language. The different basic protocols supported by the GRiSP uses port-drivers or a Native-implemented Functions (NiF), thus the code of the drivers for the different PMod accessories can also be written in Erlang and requires to seldom go back to C code level. [17]

#### 2.2 Serial Peripheral Interface (SPI)

The Serial Peripheral Interface (SPI) is used in this thesis to communicate between the *GRiSP* 2 and the Pmod UWB. It was originally designed by the company Motorola, but it became so popular that we could argue that it became a *de facto* public protocol [19]. A SPI system is composed of one master, the microcontroller providing the clock signal, and one or multiple slaves, the integrated circuits that receive the clock signal from the master [20]. It's a communication protocol that works on 4 signal lines: a clock signal (SPICLK), a slave select signal (SPICSn), a data line from the master to the slave named Master Out-Slave In (MOSI), and a data line from the slave to the master named Master In-Slave Out (MISO). The specifications of the SPI bus can vary from microcontrollers and to get the description that corresponds to a specific application one should refer to the user manual or the datasheet of the specific chip in use [19]. In this framework, the naming conventions will be the ones used in the DW1000 datasheet [3].

When the master wants to send or read requested data from a slave, it has to pull the SPICSn line, activate the clock signal on the SPICLK line, send data over the MOSI line and read the data coming from the MISO line.

#### 2.3 Pmod & DWM1000

The Pmods are modules that can be connected to the GRiSP boards with the different interfaces available. These modules can be sensors (e.g. accelerometer, temperature, ...) or actuators (e.g. RC-servos, ...). The GRiSP software provides Erlang drivers for most of the Pmods.

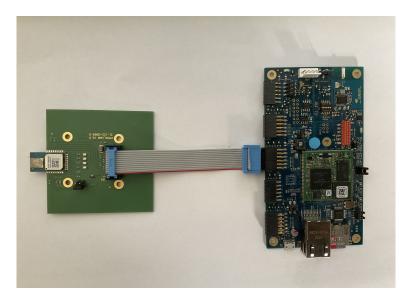

This thesis will focus on the Pmod UWB built by the company Stritzinger itself. It communicates with the *GRiSP* board through the 12 pins SPI interface of the board (SPI type 2A). The Pmod uses the DWM1000 module built by the company Decawave (now owned by the company Qorvo). The module on boards the DW1000 single chip Complementary metal–oxide–semiconductor (CMOS) UWB transceiver as well as other RF components [21]. The DW1000 like the DWM1000 is also manufactured by the company Decawave. In this thesis, even though we are working directly with the DWM1000, the actual operations are mostly performed on the DW1000.

Figure 2: DWM1000 (source: mouser.be)

Both the DWM1000 and the DW1000 are compliant with the IEEE 802.15.4-2011 UWB standard [1], which is a standard that defines the physical layer (PHY) and the MAC sublayer, for low-rate wireless personnal area networks (LR-WPAN) that are low-cost communication networks used to send data over a relatively short distance. Therefore, the physical layer of the DW1000 uses impulse radio and a modulation scheme that combines Burst Position Modulation (BPM) and Binary Phase-Shift Keying (BPSK). Additionally, the device support 6 channels, detailed in table 2.1.

| Channel number | Center frequency (MHz) | Bandwidth (MHz) |

|----------------|------------------------|-----------------|

| 1              | 3494.4                 | 499.2           |

| 2              | 3993.6                 | 499.2           |

| 3              | 4492.8                 | 499.2           |

| 4              | 3993.6                 | 1331.2          |

| 5              | 6489.6                 | 499.2           |

| 7              | 6489.6                 | 1081.6          |

| Table 2.1: DW1000 channel table (Source: DW1000 user manual [2] | 2 |  | ) |  |

|-----------------------------------------------------------------|---|--|---|--|

|-----------------------------------------------------------------|---|--|---|--|

According to the DW1000 data sheet [3], the chip can be used to determine the location of another chip to a precision of 10 centimeters. Moreover, the chip also supports concurrent data transfer and precision location. Finally, It has an extended communication range up to 290 meters at 110 kbps and with 10% packet error rate (PER)

The *GRiSP* already supports numerous pmods using SPI for communication and each one of them has its own driver code. Reading and understanding how the driver of the pmod nav and pmod dio work was one of the first steps of this work to understand the interactions between the board and the pmod over SPI.

Figure 3: The pmod uwb (left) connected to the  $GRiSP \ 2$  (right) board

#### 2.3.1 Pmod drivers architecture of the *GRiSP*

The architecture of the drivers already implemented for the *GRiSP* pmods all take advantage of the **gen\_server** behavior provided by Erlang which implements a client-server model [22]. In this model, the server manages a resource that multiple clients want to share. In our case, the driver will manage a resource, the pmod, that multiple processes can share. A client can make two kinds of requests to the server. They can make synchronous requests called *Call* or they can make asynchronous requests called *Cast*.

The gen\_server behavior also keeps in memory the server state. In the code of the pmod nav, for example, that state is used to store information like the bus used to communicate, its registers, and a cache. all related to each component of the pmod [23].

Finally, a gen\_server can be part of a supervision tree. In the case of the GRiSP, the driver processes are children of the supervisor grisp\_devices\_sup.

A supervisor is another Erlang behavior that supervises worker processes. More precisely, it keeps track of its different child processes and lets users define a restart strategy if one of them crashes [24]. Here, grisp\_devices\_sup uses the *one\_for\_one* strategy, which means that if a driver crashes, then only that one will be restarted. In other words, if the driver throws an uncaught error and stops. It is then restarted by the supervisor and there is no need to restart the *GRiSP* board manually.

#### 2.3.2 DW1000 register set

Using the SPI interface, the master device is able to access the register set of the DW1000. It is organized in multiple register files with their own size and identified with their register file IDs. The register files can be read-only, write-only, both read-write, or have a different read-write configuration for the registers that compose them (called special read/write). Some register files are also part of the double receive buffer which allows the reception of a frame while the master device is reading the previously received frame.

There are different types of register files. They can contain multiple fields and bit flags, sub-registers, or some, like the transmission buffer, contain only one field. Sub-registers are identified and can be accessed with a sub-address. They can be used in an objective to optimize the read/write operations and access only the sub-register instead of the full register file. In some cases, these sub-addresses must be used to avoid writing reserved areas within the register files.

#### 2.4 Ultra-Wideband (UWB)

According to the FCC, UWB is any signal with more than 500MHz bandwidth with a band within 3.1 and 10.6GHz that respects a specific spectrum mask. [25]. There are two types of UWB communication systems: pulse-based or multicarrier-based. Pulse-based systems generate a short burst of pulse at a specific time, while multicarrier-based uses multiple carriers at the same time to transmit the data [5].

This radio technology has multiple advantages. First, UWB is able to transmit high data rates by using very low power. Indeed, according to Shannon's formula (equation 2.1), you can increase the channel capacity C) (i.e how many bits per second can be transmitted without error over the channel) by increasing exponentially the transmitted power or by increasing linearly the bandwidth (BW)[5].

$$C = BW \log_2(1 + S/N) \tag{2.1}$$

This is very convenient for IOT devices with a small battery because they can send data with high throughput without using too much power.

Second, UWB enables location tracking with an accuracy of up to a few centimeters. In fact, one of the major features of UWB is the usage of the Timeof-Flight (ToF) to calculate the distance between devices. This method is made possible by the modulation method used to transmit the data. Since it uses narrow pulses that have clean edges, it allows determining precisely the arrival time and the distance even in the presence of multi-paths. This makes UWB 100 more precise than other technologies like Wi-Fi or Bluetooth. Moreover, due to its low latency, UWB technologies can be used for real-time location and is 50 times faster than GPS, which makes the tracking of fast-moving objects like drones possible. This technology has many applications in today's connected world. This could go from locating the key of your car in your house to locating people in a building in the case of an emergency. [6]

#### 2.5 IEEE 802.15.4-2011

The IEEE 802.15.4-2011 standard [1] defines the PHY and the MAC sub-layer for communications inside LR-WPAN which are simple and low-cost networks used to send information over a short range. The main target of this standard is devices operating in a range of 10 meters with low-data-rate wireless connectivity with low power consumption requirements. It has the capacity of using 64-bits extended address or allocated 16-bits short address, low power consumption, etc. The upper layers like the network layer or the application layer aren't described in this standard, but standards like 6LoWPAN have been developed to operate on top of IEEE 802.15.4-2011.

This section will depict the standard as it is described in the standard definition [1] and as it is used by the DW1000 and explained in the annexes of its user manual [2].

A network running the IEEE 802.15.4-2011 standard can use two types of topologies: the star topology where devices are only allowed to communicate with one central controller or the peer-to-peer topology where all devices are allowed to communicate with any other as long as they are in range.

#### 2.5.1 Ultra-Wideband PHY

The standard defines multiple PHY layers, the one that interests us in the context of this work is the UWB PHY because it is the one used by ultra-wideband devices and more particularly by the DW1000.

Figure 4: IEEE 802.15.4-2011 types of topologies (credits: IEEE[1])

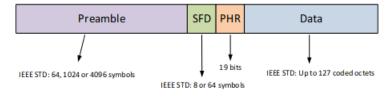

The radio signals are based upon impulse radio signaling. The modulation scheme is BPM-BPSK, a combination of BPM and BPSK, and each symbol is composed of an active burst of UWB pulses. An UWB PHY frame is composed of 3 elements: a Synchronization header (SHR) preamble, a PHR, and a data field. The SHR itself is composed of 2 elements: a sync sequence (called preamble in the DW1000 user manual) and a Start of frame delimiter (SFD).

Figure 5: UWB PHY frame structure (credits: DW1000 user manual [2])

The SHR is made of a sequence of single pulses (either positive, negative, or none) determined by a preamble code composed of ternary symbols (1, -1, 0). The standard defines two lengths of preamble code and there are between 8 and 9 different codes per length and each code can only be used on specific channels. The codes are chosen such that the resulting symbol sequence has perfect periodic autocorrelation properties. Auto-correlation is a measure used in radar technologies to measure how similar a signal is to itself [26]. But, a further explanation of this property is outside the scope of this work. Nevertheless, according to the DW1000's user manual [2], this special structure of the preamble code allows the receiver to use multi-paths as an advantage to increase the operating range and also determine the arrival time of the first path.

The SFD marks the end of the preamble. The standard describes a "short SFD" for low and medium data rates and a "long SFD" used for faster data rates. Furthermore, the reception of the SFD marks the switch into BPM-BPSK modulation. When it comes to the DW1000, this event is used for the time-stamping of the reception of the frames. Indeed, the timestamp can be determined with high accuracy due to its deterministic characteristics combined with the determination of the first arriving ray [2].

After the SHR comes the PHR, it contains, among other fields, the length of the frame payload and it uses 6 parity bits (Single-error-correction double-error-detect (SECDED)) to detect any channel errors during its transmission

| Bit<br>0   | 1  | 2  | 3  | 4  | 5  | 6  | 7                 | 8                   | 9              | 10  | 11         | 12   | 13    | 14     | 15  | 16 | 17 | 18         |

|------------|----|----|----|----|----|----|-------------------|---------------------|----------------|-----|------------|------|-------|--------|-----|----|----|------------|

| <b>R</b> 1 | R0 | L6 | L5 | L4 | L3 | L2 | L1                | L0                  | RNG            | EXT | <b>P</b> 1 | PO   | C5    | C4     | C3  | C2 | C1 | <b>C</b> 0 |

| Dat<br>Rat |    |    |    |    |    |    | Ranging<br>Packet | Header<br>Extension | Pream<br>Durat |     |            | SECI | DED C | heck B | its |    |    |            |

Figure 6: PHR bit description (credits [1])

Finally, the last part of the UWB PHY is the actual data payload. It has a maximum size of 127 bytes. Like the PHR it is encoded using BPM-BPSK modulation and uses Reed Solomon code as Forward error correction (FEC). This section of the frame can be transmitted at data rates of 110 kbps, 850 kbps, 6.8Mbps, or 27Mbps (however, the DW1000 doesn't support a 27Mbps data rate).

#### 2.5.2 MAC sub-layer

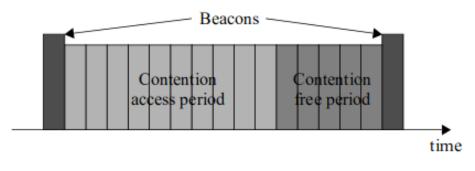

The MAC sub-layer is situated above the UWB-PHY layer. It is responsible, among other tasks, to manage the access to the radio channel. It also provides multiple features like beacon management, acknowledgment, etc. One possible option for the Personal Area Network (PAN) coordinator to control channel access is to use a superframe structure to bind the channel times. A superframe is delimited by beacon frames sent by the coordinator. The beacon frame is used to identify a PAN, synchronize the devices inside a PAN, and defines the structure of the superframe. A superframe can be divided into two parts. First, the contention access period (CAP), where devices compete with each other to communicate and use slotted Carrier-sense multiple access with collision avoidance (CSMA-CA). Second, the contention-free period (CFP), always situated at the end of the superframe, enables the coordinator to allocate guaranteed time slots (GTS) for applications with special needs like low-latency applications. Figure 7 shows an example of the structure of a superframe.

The MAC frames are put inside the data payload field of the UWB-PHY layer. A MAC frame is composed of three elements: a MAC header (MHR), a MAC

Figure 7: MAC Superframe (credits [1])

payload, and a MAC footer (MFR).

|                  |                    | N                             | /IAC Header (N         | MAC Payload              | MAC Footer<br>(MFR) |                            |                              |             |

|------------------|--------------------|-------------------------------|------------------------|--------------------------|---------------------|----------------------------|------------------------------|-------------|

| Frame<br>Control | Sequence<br>Number | Destination<br>PAN Identifier | Destination<br>Address | Source PAN<br>Identifier | Source<br>Address   | Aux Security<br>Header     | Frame Payload                | FCS         |

| 2<br>octets      | 1<br>octet         | 0 or 2<br>octets              | 0, 2 or 8<br>octets    | 0 or 2<br>octets         | 0, 2 or 8<br>octets | 0, 5, 6 10 or 14<br>octets | Variable number of<br>octets | 2<br>octets |

Figure 8: MAC frame and its fields (credits [2])

| Bit         | Bit                 | Bit              | Bit            | Bit                | Bits     | Bits                     | Bits             | Bits                      |

|-------------|---------------------|------------------|----------------|--------------------|----------|--------------------------|------------------|---------------------------|

| Oto         | 3                   | 4                | 5              | 6                  | 7 to 9   | 10 & 11                  | 12 & 13          | 14 & 15                   |

| Fran<br>Typ | Security<br>Enabled | Frame<br>Pending | ACK<br>Request | PAN ID<br>Compress | Reserved | Dest.<br>Address<br>Mode | Frame<br>Version | Source<br>Address<br>Mode |

Figure 9: The frame control of the MAC header and it (credits [2])

The MHR begins with a two bytes frame control field. It is there to identify the type of the frame and the structure of the MAC header. As figure 9 shows, the first three bits of the frame control indicate the type of frame. A frame can be of type beacon (2#000), data (2#001), acknowledgement (2#010), or MAC command (2#011) while the other value (2#1xx) are reserved. Bit #3 indicates if there are auxiliary security headers in the frame. Bit #4 indicates if there is more data to receive. Bit #5 specifies if the transmitter of the frame is expecting an acknowledgment from the receiver. Bit #6 is the PAN compression field. When it is set to one and both the destination and source addresses are present, only the destination PAN ID is present in the MAC header and the source PAN ID is assumed to be equal. Bits #7-9 are reserved. Bits #10-11 and Bits #14-15 are address compression fields. If their values are set to 2#00, then their corresponding PAN ID and address are not present in the MAC header. If their values are set to 2#10, then their corresponding address is a short address (16 bits). Finally, 2#01 is reserved and shouldn't be used, if their values are set to 2#11 then their corresponding address (64 bits).

Finally, the MAC frame is ended by the MFR which is two bytes long and is in fact a frame checking sequence (FCS) CRC used to determine if the frame is corrupted or not.

# Chapter 3 Implementation of the driver

This chapter explains how the driver was built starting from the setup of the SPI clock and performing data exchange on the SPI line. Before performing read and write operations, and finally, being able to send and receive data using UWB. The file containing the API of the driver is called pmod\_uwb.erl and is present in the appendix A.

#### **3.1** Interaction with the pmod

Before interacting with the board, we have to determine the communication mode (i.e. SPI mode) defined by the pair of parameters: clock polarity (SPIPOL) and clock/data phase (SPIPHA). The SPIPOL determines on which level the clock idles while the SPIPHA will determine which operation is performed on each edge of the clock [19]. Table 3.1 describes the different SPI modes possible.

| SPIPOL | SPIPHA | SPI<br>mode | Description (from the master point of view)         |

|--------|--------|-------------|-----------------------------------------------------|

| 0      | 0      | 0           | Data is sampled on the rising (first) edge of       |

| 0      | 0      | 0           | the clock and launched on the falling (second) edge |

| 0      | 1      | 1           | Data is sampled on the falling (second) edge of     |

| 0      |        | 1           | the clock and launched on the rising (first) edge   |

| 1      | 0      | 2           | Data is sampled on the falling (first) edge of      |

| 1      | 0      | Z           | the clock and launched on the rising (second) edge  |

| 1      | 1      | 3           | Data is sampled on the rising (second) edge of      |

|        |        | 0           | the clock and launched on the falling (first) edge  |

Table 3.1: Different SPI modes (source: DW1000 data sheet[3])

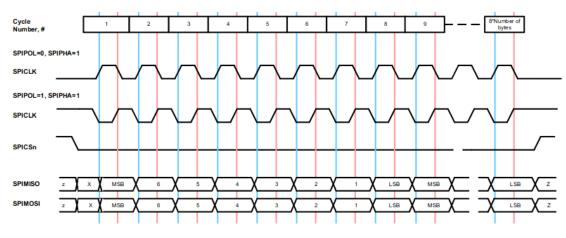

Figure 10 shows the two possible interactions with the DW1000 when the SPIPHA is set to 1. The blue line represents when the data is launched and the red line represents when it's sampled on the MISO and MOSI lines.

Figure 10: DW1000 - SPIPHA = 1 (source: DW1000 data sheet [3])

If these settings are not set correctly, the data sent over the different lines won't be correctly interpreted at the other endpoint. For example, if the polarity isn't set correctly, we could observe a bit shift between the expected data and the actual value read by the GRiSP.

On the DW1000, these parameters can be set through the pin GPIO5 for SPIPOL and GPIO6 for SPIPHA. Thus, we have to check the schematics of the pmod UWB to see their inputs. In this case, both GPIO5 and GPIO6 are plugged into a 3V. Therefore, SPIPHA and SPIPOL both have a value of 1. Both of these pins are only sampled on the rising edge of the RSTn, which means that this pin should be pulled at the startup of the driver to configure correctly the clock settings. However, the DW1000 datasheet [3] states that this pin should be configured as high impedance, but the current GRiSP Erlang runtime library doesn't support this kind of setting yet. Consequently, since we are not able to pull the RSTn pin, SPIPOL and SPIPHA are never sampled and their values are equal to "0". Therefore the SPI mode is the number 0 where data is sampled on the rising edge of the clock and launched on the falling edge.

In the driver code, the SPI mode is represented by a record given at each transaction call.

#### -define(SPI\_MODE, #{clock => {low, leading}}

Listing 3.1: SPI\_MODE macro used to define the clock settings

When those values are set, we are ready to perform our first transactions on the SPI.

#### 3.1.1 Transaction format

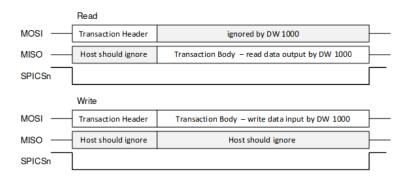

A transaction can be divided into 2 parts.

The first one, the transaction header, contains information about the type of transaction (either read or write), the register file targeted by the operation, and an eventual offset/sub-addressing.

The second one, the transaction body, contains either the data read from the DW1000 or the data that has to be written on the DW1000. In the case of a write operation, both parts are sent by the master. Otherwise, in the case of a read, the transaction header is sent by the master, and the transaction body is sent by the slave. Figure 11 gives a visualization of the different transactions.

Figure 11: Different SPI transactions (source: DW1000 user manual [2])

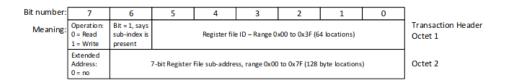

There are three types of headers that can be used to communicate with the DW1000. The first header (figure 12) is only one byte long. Bits 0-5 contain the register file ID, a hexadecimal value that identifies each register file of the DW1000. Bits #6 indicates if the header contains a sub-address. In the case of this header, its value is set to 0. Bit #7 indicates the type of operation.

Figure 12: One byte header (source: DW1000 user manual [2])

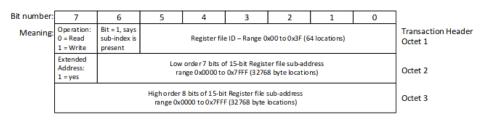

The second header (figure 13) is two bytes long and gives a short sub-indexing that indicates a sub-address in the register file. The first byte of this header is similar to the previous one except that bit #6 has now a value of "1" to indicate that a sub-index is present. Bits 0-6 of the second byte specify the short sub-indexing (ranges from 0x00 to 0x7F) and bit #7 which indicates that we are using an extended address is set to "0" for the 2 bytes header.

Figure 13: Two bytes header (source: DW1000 user manual [2])

The last header (figure 14) is three bytes long and gives a long sub-indexing which gives the possibility to use sub-addresses up to a value of 0x7FFF. To use this header, bit #7 of the second byte should be set to "1".

Figure 6: Three octet header of the long indexed SPI transaction

Figure 14: Three bytes header (source: DW1000 user manual [2])

#### 3.1.2 Example

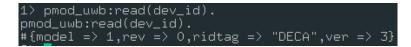

Let's take the example of a read operation performed on the register  $DEV_ID$ . This register is the device identifier and is hard-coded into the silicon of the chip. That makes it the perfect register to test how the driver interacts with the chip through the SPI interface because the expected result of the interaction is predictable. Furthermore, the user manual gives exactly the description of the transaction (Figure 15)

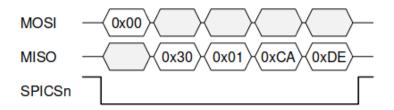

Figure 15: Description of a read operation performed on the DEV\_ID register (source: DW1000 user manual [2]

Figure 16: Read transaction on DEV\_ID showed on the logic analyser

Figure 16 shows the output of a logic analyzer during a read operation on  $DEV\_ID$ . The logic analyzer is able to sample the different SPI lines and display the evolution of their values over time.

Channel 0, the first row is SPICSn. We can see that when the transaction starts, the line is pulled down and when the transaction is done, the line is pulled back up.

Channel 1 is the MOSI line. The first byte has a value of 0x00. This is the transaction header. Its value tells us that the operation is a read operation (bit #7 has value 0), without sub-index (bit #6 has value 0) on the register file  $DEV_ID$  which has the ID value of 0 (bits #5-0 have a value of 0). The 4 bytes following the header all have a value of 0xFF and should be ignored because a read operation is performed.

Channel 2 is the MISO line. The first byte has a value of 0xFF and should be ignored. Then the last three bytes sent by the pmod have a value of 0x3001CADE which is the value we are expecting to read from the register file.

Channel 3 is the SPICLK. We can clearly see for each byte of the transaction, eight pulses corresponding to the eight bits being sent or received over the MOSI or the MISO lines.

#### 3.2 Mapping the registers

The second step of building the driver was to map the register to allow a user to read and write values from them. This part needs to be written with a lot of rigor because it this the stepping stone of all the operations that can be made on the pmod.

In the driver previously implemented by the *GRiSP* team, the pmod\_nav and the pmod\_dio are also using the SPI interface which was a great starting point to

understand how the driver had to be built. Even though the approaches of the two drivers are different, they both use Erlang maps as output to store the values read from the pmod or as input to store the values that have to be written. Since both driver approaches were equivalent and the pmod\_dio was easier to understand, it was decided to use the same approach for the mapping of the DW1000. For example, the result of a read operation on the register file  $DEV_ID$  is: #{ridtag => "DECA", model => 1, ver => 3, rev => 0 } and if we want to write the value "1" in the sub-register TXSTRT of the register file  $SYS_CTRL$ , then the following map needs to be given in the arguments of the write API call: #{ txtstrt => 2#1 } (Note that the value is written in the binary form but it can also be written in the decimal form).

Additionally, as we are about to see in the following sections, the DW100 contains different types of registers. In the process of writing the driver and its API, extra care has been taken to write a consistent read/write API for every register file to make the implementation more user-friendly.

#### 3.2.1 Errors in the user manual

During the mapping of the register, a few errors were noticed in the user manual of the DW1000 [2], here is the list of all of them and how they were solved:

- In the register map overview, the length of the register file DRX\_CONF is 44 bytes. However, the sum of the size of the sub-registers present in the overview of the register file is 45 bytes. In the API provided by Qorvo [8], the size of the register file is also 44 bytes but one sub-register with a length of one byte, RXPACC\_NOSAT isn't present. Since the API provided by Qorvo works and got tested, the information contained inside should overrule the ones in the user manual. Thus, its version got used in the driver of the pmod.

- In the user manual as well as in the API, the size of the register file  $RF\_CONF$  is set to 58. However, if we take the offset of the last sub-register *LDOTUNE* and add its size, 5 bytes, we reach an offset of 0x35 or 53 in decimal. To match the information provided by the chip manufacturer and to compensate for the 5 remaining bytes, a placeholder was introduced at the end of the register file in its mapping.

- The subregister *RF\_CONF* has a size of 3 bytes in the user manual, but in the API, it has a size of 4 bytes. In the driver of the pmod, its size has been set to 4 bytes too.

- In the user manual and the API, the size of the register file  $TX\_CAL$  is 52 bytes. Yet, when we sum the size of all its sub-registers, we obtain a size of

12 bytes. Since the difference was too big, no placeholder got introduced and the size of the register is set to 12 bytes in the pmod driver

- The size of *OTP\_IF* in the register overview as well as in the DW1000 API is set to 18. However, if we sum the size of its subregisters given in the user manual and also in the API, we reach 19 bytes. Thus, in the driver, the size has been set to 19 bytes too.

- The register file with the ID 0x2E has two names in the user manual. In the register map overview, it's called *LDE\_CTRL* but in its description, it's called *LDE\_IF*. Additionally, in the API of the driver provided by Qorvo, only *LDE\_IF* is used. However, to avoid any confusion for a user, both names are accepted by the driver of the pmod.

- The size of *DIG\_DIAG* given in the user manual and the API is 41 bytes. Nevertheless, the sum of the size of all its subregisters is equal to 38. Thus, this value was used in the driver

- The size of *PMSC* given in the user manual and the API is 48 bytes. However, if we sum the size of all its subregisters we reach a value of 41 bytes. Additionally, if we try to compute its size by checking the last offset of its subregister we reach 0x2B which is 43 in decimal. In the driver of the pmod, the used size is 43 bytes.

#### 3.2.2 Read the registers

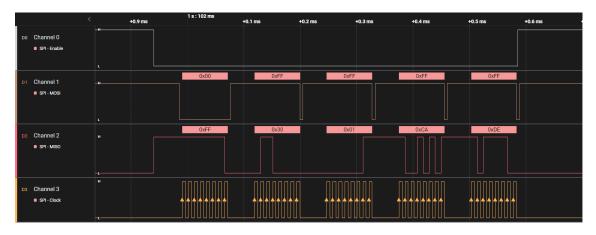

The API function to read a register is **read/1**. Its only parameter is an atom corresponding to the mnemonic of the register file we are trying to access. It will return a map of the different elements stored inside the register file and their values. Figure 17 shows an example of an API call for the register file *DEV\_ID* and the returned value

Figure 17: Read API call on register *DEV\_ID*

This function will send a request to the gen\_server of the driver which will internally call the function read\_reg/2. Its first parameter Bus is a reference to the opened SPI bus stored in the internal state of the gen\_server. The second parameter is again the mnemonic of the register file we are trying to access. This internal function will call the function header/2 which builds the header of the transaction and returns it in binary format. It then calls grisp\_spi:transfer/2 that returns the value contained in the register file in an Erlang bitstring format. Finally, the content of the bitstring is decoded using the function reg/3 which performs a pattern matching on the different fields contained in the bitstring and then stores them in a map.

It is important to note that the value returned by the pmod UWB are sent in little-endian and the default configuration of Erlang interprets bytes in big-endian. Therefore, for most of the registers, the byte order needs to be reversed before decoding them.

During the implementation, the choice was made to read register files fully and not letting the possibility for users to read individual sub-registers. The goal here was to have a reliable operation without performing any optimization using the register offsets as little as possible.

There are two special register files that have to be processed differently than others. First,  $TX\_BUFFER$  is a write-only register, and reading its value during transmission could corrupt its values. Therefore, an error is thrown if read\_reg/2 is called with tx\_buffer is passed in the second parameter. Second, the  $LDE\_IF$  or  $LDE\_CTRL$  register has a size of 10Mb, and only 8 sub-registers are documented in the user manual with gaps that can reach 1026 bytes. Therefore, the choice was made to read each sub-register individually using the offsets of the different sub-registers and merge the results.

#### 3.2.3 Write the registers

The API function to write a value in a register file is write/2. The first parameter is like in the write operation the mnemonic of the register file we are trying to access. The second parameter is a map similar to the one returned in the read operation but only containing the value the user wants to change.

2> pmod\_uwb:write(panadr, #{pan\_id => 16#DECA}).

Figure 18: Write API call on register PANADR

3> pmod\_uwb:write(pmsc, #{pmsc\_ctrl0 => #{sysclks => 2#01}}).

Figure 19: Write API call on register PMSC

Figure 18 and 19 show 2 examples of a writing operation on the pmod. The first one shows the operation on a "simple" register containing only two sub-fields:  $PAN\_ID$  and  $SHORT\_ADDR$ . Since  $PAN\_ID$  is the only sub-field present in the map, the write operation will only modify that sub-field.

The second one performs the operation on a register file with a more complex structure. Indeed it is composed of multiple sub-registers containing multiple sub-fields. This is reflected in the map given in the parameter of the function by having a bigger depth than the one in Figure 18. Here, the write operation will be operated in the sub-register  $PMSC\_CTRL0$  of the register file PMSC by changing the value of the sub-field SYSCLKS by the binary value "01". Additionally, it is also possible to write inside multiple sub-fields of one register and also in multiple sub-registers in the same API call shown in figure 20

Figure 20: Write API call on register  $\ensuremath{\textit{PMSC}}$  on multiple sub-registers and subfields

When a user wants to write a value in a register file, we must be careful to not overwrite values that are already present in the register file. Due to the nature of the SPI transaction, the minimum amount that someone can read or write from the device is one byte. This implies that if someone wants to change the value of a bit flag we need to write, at the minimum, 7 other bits that the user doesn't want to change. Thus we have to read their value first and write the same values alongside the changed bit flag. In the driver, in most of the cases, the choice was made that when the user wants to change a value inside a register file, the whole register file will be read and written again with the changed value. In some cases, this is not possible because of the configuration of the register file. Indeed, some register files either have read-only sub-register (for example  $AGC\_CTRL$ ) or reserved bytes that can't be overwritten (for example  $EXT\_SYNC$ ). In this case, each of their sub-registers is written individually. Additionally, since all of the sub-registers of these special register files are longer than one byte, instead of writing again all their values at each write, only the sub-registers targeted by a write will be written.

However, due to the choice that was made in the reading operation of only allowing reading register files in their entirety, we need to read the whole register file containing the sub-register and extract its values. Furthermore, since there is no guarantee that the values of a sub-register don't change between writes, the register file needs to be read each time we want to write in one of its sub-register. In other words, if a user wants to write simultaneously (i.e. on the same API call) inside n sub-registers, then the corresponding register file will be read n times.

Additionally, some register files like  $RX\_BUFFER$  are read-only register files. If the user tries to write in those register files, an error will be thrown to protect their values.

Finally, the transaction body should be sent in little-endian. Thus, when the data is sent on the SPI interface, we must be sure that the endianness of the bytes has been changed.

#### **3.3** Initialization of the pmod

After the startup of the  $GRiSP \ 2$  board, the driver needs to be loaded and the DW1000 needs to be initialized. This section describes the different steps and how the initialization has been implemented.

#### 3.3.1 Checking the connected device

The first thing to do during the loading is to check if the user selected the correct slot of the  $GRiSP\ 2$  and connected the right pmod to it. After adding the driver process to the supervisor and opening the SPI bus, the driver checks the content of the register file  $DEV_ID$  with the ID 0x00. This read-only register file contains the register identification tag and model. With these 2 registers, we are able to check if the device is connected to the right device, the DW1000. Indeed the value of RIDTAG is constant over all Decawave parts and should always be 0xDECA and the value of MODEL should be 0x01 for the DW1000. If one of the values is different from the one expected, the driver throws an error and the initialization stops there.

#### 3.3.2 Loading the leading edge algorithm

After checking if the connected device is the right one. The leading edge detection algorithm needs to be loaded from the ROM of the DW1000. This algorithm is responsible to find the first path of a transmitted message and to compute the timestamp of the reception. If the algorithm isn't loaded, it is still possible to perform message transmission if we deactivate the leading edge detection before the first reception. In that case, the RX timestamp won't be correct. Thus some algorithms like two-way ranging can't be performed because it relies on the timestamps to perform their measurements. Loading the algorithm from the ROM is done by following a precise procedure described in the user manual of the chip [2] and also in the examples for the C driver made by the company. Extra care must be taken when performing this operation because if the algorithm is activated but not loaded correctly at the reception of a packet, the chip can have unexpected behavior and get stuck in an undocumented state where data reception isn't possible anymore.

To load the algorithm, first, the value 0x301 needs to be written in the  $PMSC\_CTRL0$  sub-register of the PMSC register file. This writes the value 0x01 SYSCLKS and sets the value an undocumented bit to 1. Then, the value 0x8000 needs to be written in the sub-register  $OTP\_CTRL$  which sets the value of the bit flag LDELOAD to 1. This will copy the microcode from the ROM to the RAM. Finally, the value 0x200 needs to be written in the sub-register  $PMSC\_CTRL0$

which puts sets back SYSCLKS to automatic mode and sets back the value of the undocumented bit to 0.

#### 3.3.3 Writing optimal values

When the DW1000 turns on, some of the default values aren't set up on optimal values for performances. It is the job of the driver designer to overwrite these values before using the chip to send frames. The user manual describes how to perform that initialization if we use the default configuration of the chip. Since it was decided to stick with these default values, the driver follows those instructions, but if one decides to change the default transmission channel for example, other values should be written for optimal operations. Table 3.2 shows the different sub-registers to overwrite and the values that have to be written inside if we keep the default configuration of the DW1000.

| Register file | Sub-register    | Default value | New value        |  |

|---------------|-----------------|---------------|------------------|--|

| AGC_CTRL      | AGC_TUNE1       | 0x889B        | 0x8870           |  |

| AGC_CTRL      | AGC_TUNE2       | /             | 0x2502A907       |  |

| DRX_CONF      | DRX_TUNE2       | 0x311E0035    | 0x311A002D       |  |

| LDE_CFG       | LDE_CFG1        | 0xC           | 0xD              |  |

| LDE_CFG       | (NTM sub-field) | UXC           |                  |  |

| LDE_CFG       | LDE_CFG2        | 0x0000        | 0x1607           |  |

| TX_POWER      | N/A             | 0x1E080222    | 0x0E082848       |  |

| RF_CONF       | RF_TXCTRL       | DE1E3DE0      | 0x001E7DE0       |  |

| TX_CAL        | TC_PGDELAY      | 0xC5          | $0 \mathrm{xB5}$ |  |

| FS_CTRL       | FS_PLLTUNE      | 0x46          | 0xBE             |  |

Table 3.2: All the default values to overwrite

#### 3.3.4 Writing custom configuration

After writing the optimal values, we still have to write some custom configurations that are either related to the pmod in itself or enable elements that are not turned on by default. The following list gives an explanation of each setting and its different effects.

1. Setting the sub-field PLLLDT to "1" to ensure that the PLL locks flags work correctly. The goal of this operation is to have better debugging and diagnostic capacities when a frame isn't correctly sent or received.

- 2. Setting the sub-fields *MSGP2* and *MSGP3* of the sub-register *GPIO\_MODE* to "01". It indicates that the GPIO pins 2 and 3 are respectively operating as RXLED output and TXLED output.

- 3. Setting the sub-fields *MSGP0* and *MSGP1* of the sub-register *GPIO\_MODE* to "01". It indicates that the GPIO pins 0 and 1 are respectively operating as RXOKLED output and SFDLED output.

- 4. Setting the sub-fields *GPDCE* and *KHZCLKEN* to a value of "1". *GPDCE* serves to enable the clock in charge of the feature that makes the LEDs blink. *KHZCLKEN* enables the kilohertz clock used by the same feature.

- 5. Setting the sub-field *BLNKEN* to a value of "1". Alongside the setup made in the three previous points, this bit enables the LED blinking functionality of the pmod. Even though they increase power consumption, being able to observe the LEDs blinking is a nice feature to have during development and especially when debugging.

- 6. Setting the value of the sub-field  $EVC\_EN$  to "1" to enable event counters such as  $EVC\_FFR$  which indicates the number of frames rejected by the frame filtering function. These counters are also great tools to have during debugging because they allow us to see what happened after a series of transmissions.

- 7. Setting the value of the sub-field TXPSR to "2#10" which changes the preamble symbols to 1024. This change is made because without modifying the preamble symbols settings, the auto-acknowledgment feature used in section 4 can't work.

#### 3.3.5 Setting up SFD

As we've seen in the previous sections, the physical layer of IEEE 802.15.4 is divided into multiple fields. Among them, the SFD sequence marks the end of the preamble of the frame. The DW1000 manages that part of the physical layer by itself when we want to send a frame. However, if the auto-acknowledgment is the first frame transmitted after startup, the SFD sequence won't be initialized because its initialization is only done at the first user transmission request. Therefore, if we want the auto-acknowledgment to work right away after startup we need to trigger the loading of the sequence. The user manual explains that the most efficient way to perform that is to "simultaneously initiate and abort a transmission" which resolves into setting the value of the flags TXSTRT and TROFF to "1" simultaneously. Figure 21 shows how this operation is performed by the driver. Figure 21: Setup of the SFD inside the code

#### 3.4 Transmission

The transmission and reception of UWB-PHY frames are the highest-level operations provided by the driver. At this level, it only treats the data payload as one single block of data that should be transmitted or received. It's the role of the higher layers to manage the eventual content and the structure of the payload. This section will explain in detail how these two operations are actually performed by the driver.

#### 3.4.1 Sending a frame

The procedure to send a UWB-PHY frame is the following. First, we have to write the data inside the subregister  $TX\_BUFFER$ .

Second, we have to set the value of a couple of sub-fields inside the register file  $SYS\_CTRL$ . The sub-register TXBOFFS allows the user to specify an offset inside the transmission buffer indicating the first byte of the PHY payload. This allows further optimization but isn't used here and its value is set to 0. We also have to set the value of the sub-field TFLEN which indicates the size of the data portion of the frame plus a two bytes CRC. The DW1000 takes care of the computation of the CRC and **replace** the last two bytes of the payload by the newly computed CRC. Thus if we don't add these two bytes to the value written inside TFLEN, the actual data we are trying to send will be shortened by two bytes.

Third, we can trigger the start of the transmission by the DW1000 by writing the value "1" inside the sub-field TXSTRT of the register file  $SYS\_CTRL$ .

Finally, we have to make sure that the transmission occurred correctly. This can be done by checking the event status bit TXFRS ("transmit frame sent") of the register file  $SYS\_STATUS$ . This verification is performed by a recursive function. This function does a read request on  $SYS\_STATUS$  and checks the value of TXFRS. If it is set to "0", then a recursive call is performed. Otherwise, if the value is set to "1", then the function returns ok and stops. The whole operation is operated synchronously and the calling API function won't return before the transmission has been performed.

At this stage, waiting for the completion of the transmission might seem useless because the frame is transmitted right away. However, in the case where frames are sent with a delay, this functionality is useful to avoid performing other operations (e.g. turning on the receiver) before the actual transmission of the frame.

On the driver, there are two functions available in the API: transmission/1 and transmission/2. They both take a bitstring in their first parameter but the second function allows the user to specify options for the transmission while the first one will use the default settings.

There are four options possible to set:

- wait4resp: It indicates that the receiver should be turned on after the transmission of a frame. The DW1000 will clear the bit after enabling the receiver, thus this setting must be set at every transmission of a frame that requires it. By default, this option is disabled.

- w4r\_tim: It specifies the delay in microseconds between the transmission of a frame and the automatic enabling of the reception if wait4resp is enabled. This is useful in the case where some kind of delay between a request frame and its response is known (for example in the double-sided two-way ranging). It is set by default at 500µs and only used when wait4resp is enabled.

- txdlys: It enables the "transmitter delay sending" setting used to control precisely the transmission of a frame at a time specified in tx\_delay. it is by default disabled and should be enabled for every transmission that requires the setting.

- tx\_delay: It specifies the exact clock time when the transmission of the next frame should occur if txdlys is enabled. These two options are useful when the program needs to know the exact transmission time of a transmission.

These options are specified at the time of transmission for two reasons. First, this gives one more layer of abstraction which relieves the user from writing directly inside the register files.

Second, and most important, WAIT4RESP and TXDLYS are both bits that should be written at the same time (i.e. in the same SPI transaction) as TXSTRT.

In the beginning, the API was also able to take a String in the data argument. It was really useful in the first stages of the implementation of the transmission for testing purposes. However, as the development of the driver made progress, that option became more and more useless and was finally dropped from the API in the later versions

#### 3.4.2 Receiving a frame

To perform a reception with the pmod UWB, the user can call two functions: transmit/0 and transmit/1. The first one is a simplification of the first one by

setting to false by default the parameter of the second one. This parameter: RXEnabled specifies if the reception has been enabled prior to the function call. This is because in some cases the reception can automatically be turned on after the transmission of a frame. This parameter is there to avoid trying to enable the reception a second time which might trigger some event status bit specifying an error during the reception of the frame before receiving the actual frame.

On the DW1000, the reception can be divided into different steps described in the DW1000 user manual [2]:

- 1. Preamble detection: During that period, the device will try to detect the preamble sequence by cross-correlating chunks of the preamble symbols. It is possible to enable and set a timeout to allow the receiver to stop the detection of the preamble. If the timeout is triggered, the event status bit *RXRFTO* will be set to "1" and the reception will be aborted. Otherwise, if it isn't enabled or isn't triggered, *RXPRD* is set to "1" and the procedure continues to the next step

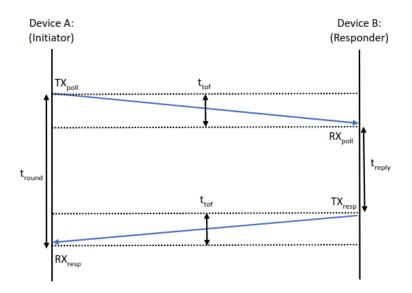

- 2. Preamble accumulation and SFD detection: after the detection of the preamble, the device will accumulate the preamble symbols and look for a particular sequence of symbols, the SFD. If the SFD isn't detected before a certain time after the detection of the preamble, the reception is aborted and *RXSFDTO* is set to "1". Otherwise, *RXSFDD* is set to "1" and the process moves to the next step.